## DDR3 Case Study – High Speed Design Services, LLC

John Medina PCB Layout Engineer High Speed Design Services, LLC

Kim Owen Signal Integrity Engineer High Speed Design Services, LLC

#### Audience and why you may be interested in this presentation

#### PCB Designers

- CES experience?

DDR3 routing and rule definition experience?

LVDS Differential routing experience?

High Pin count BGA breakout experience?

#### Electrical Engineers

Do you define your specific design case timing and noise budgets based off simulations?

USERZUSE

Knowledge of High Speed PCB Process?

#### HSDS Offers:

High Speed PCB Layout Class

Signal Integrity Class

# DDR3 Case Study - Layout and Signal Integrity practices should be combined to deliver high-performance PCB designs

#### **Objectives**

- Review best practices used in high speed

PCB design Layout

- To show how the collaboration of these best practices of layout and SI can lead to successful PCB designs

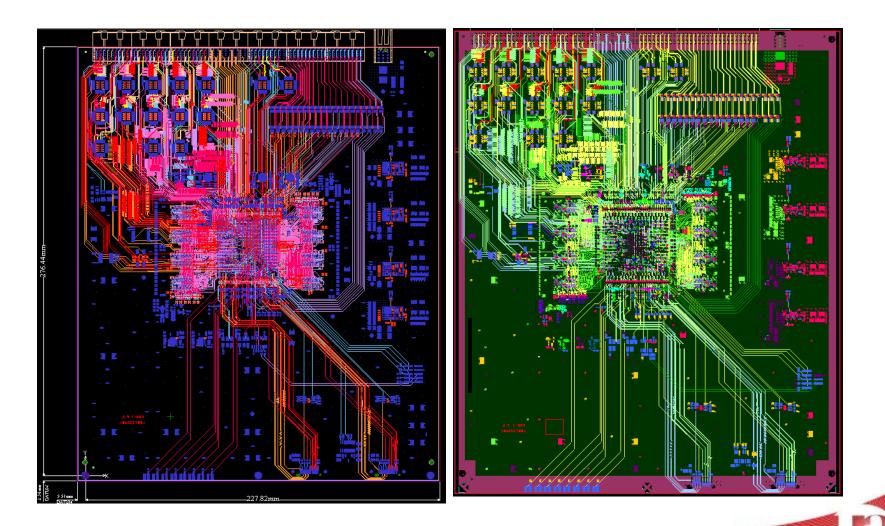

- Highlights of actual working DDR3/LVDS SERDES design

#### Results

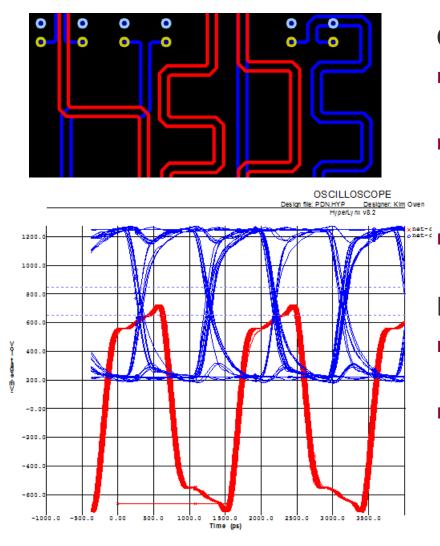

- HyperLynx simulations and PCB design lessons learned

- Proven High Speed Process benefits are identified and featured

## **DDR3 Case Study Agenda**

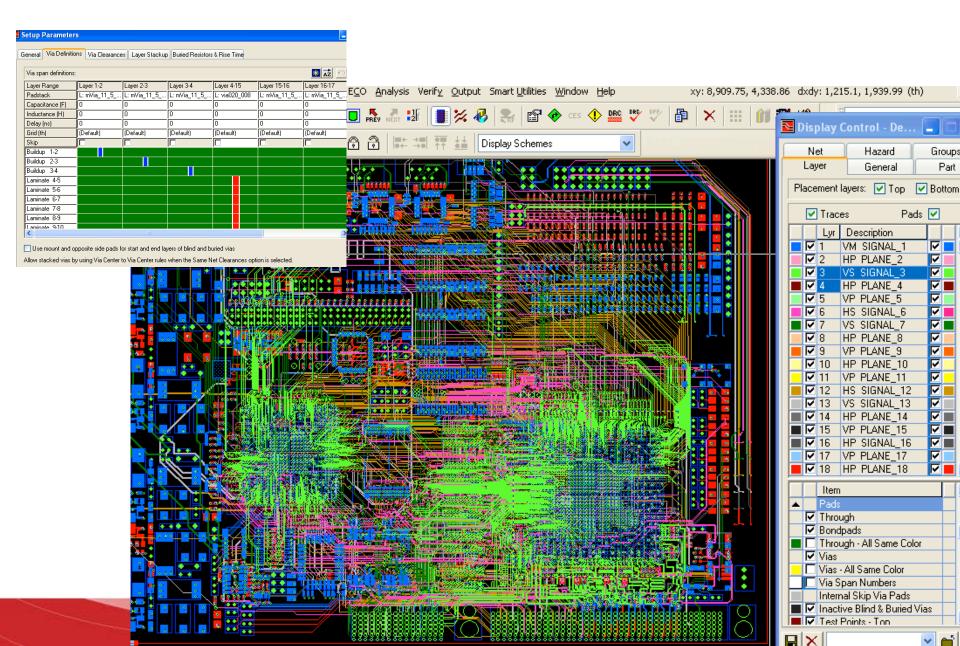

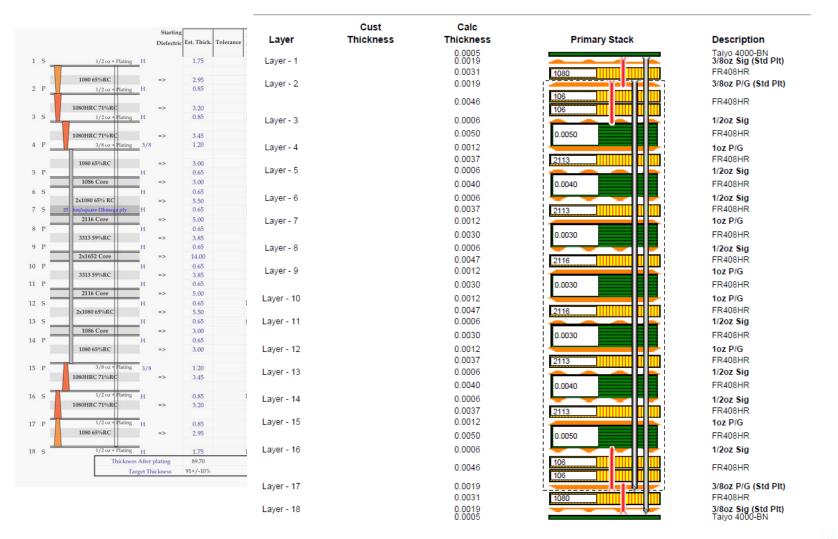

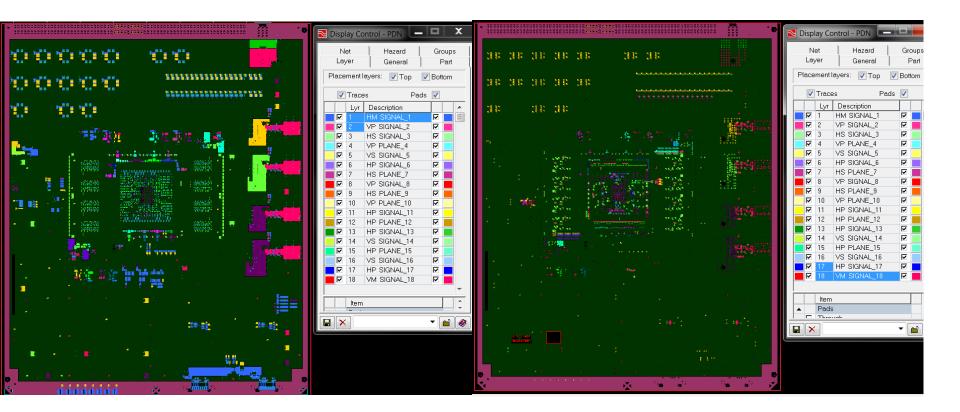

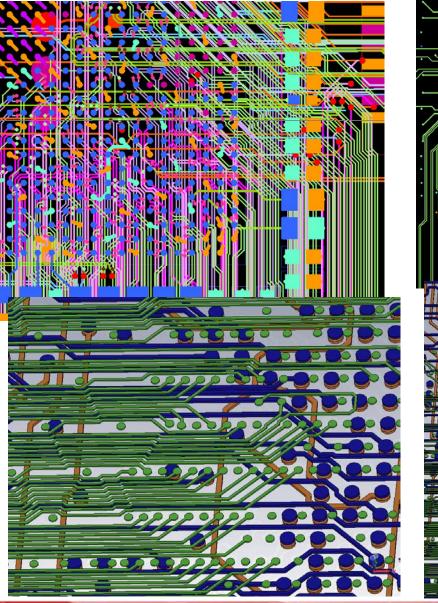

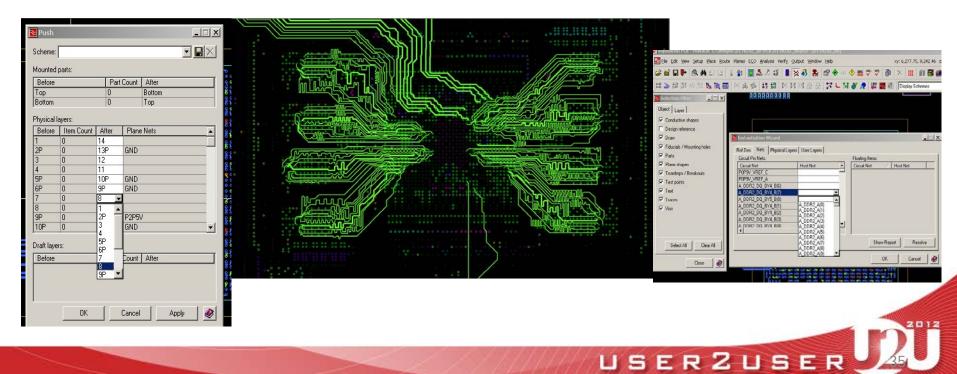

- Review of HDI High Speed Stackups and benefits.

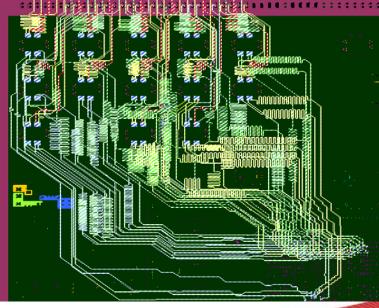

- How to breakout high pin count BGA's. Power Planes and examples reviewed.

- IOD techniques and best practices

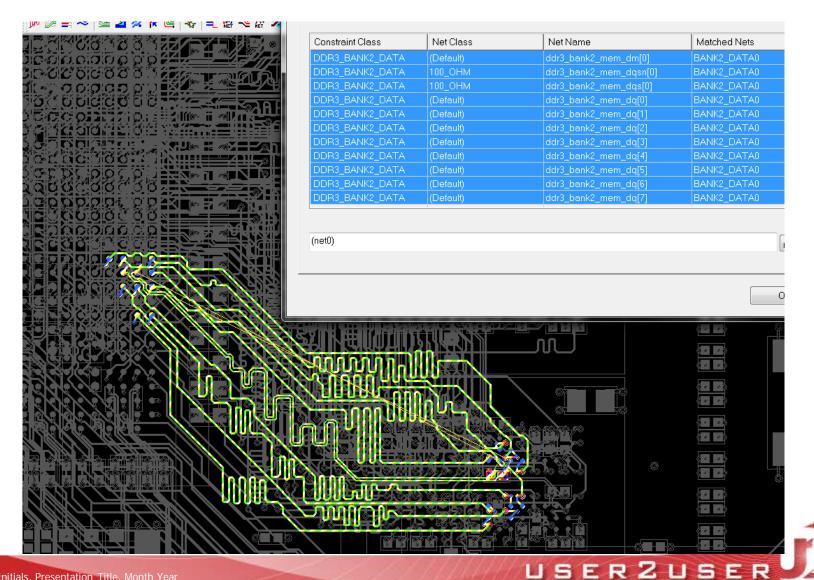

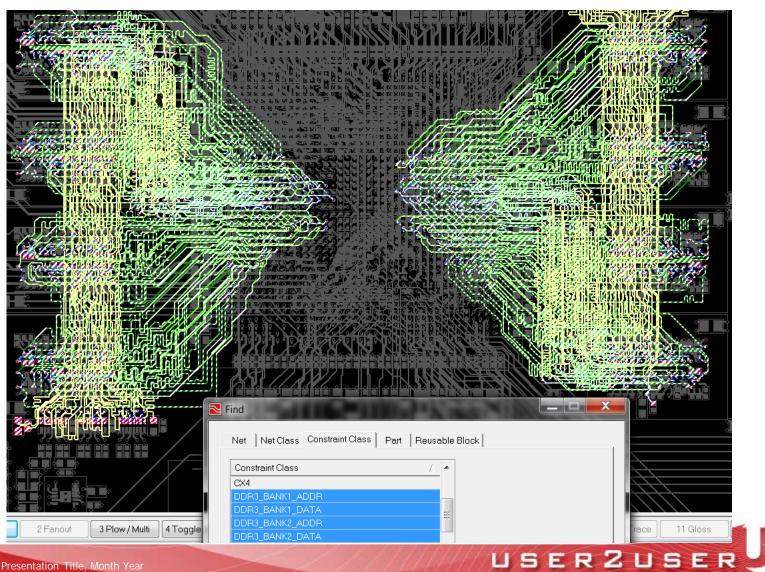

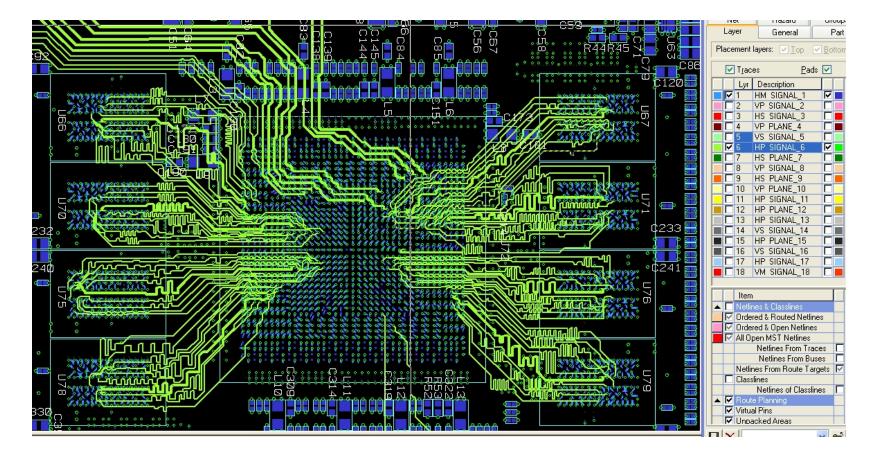

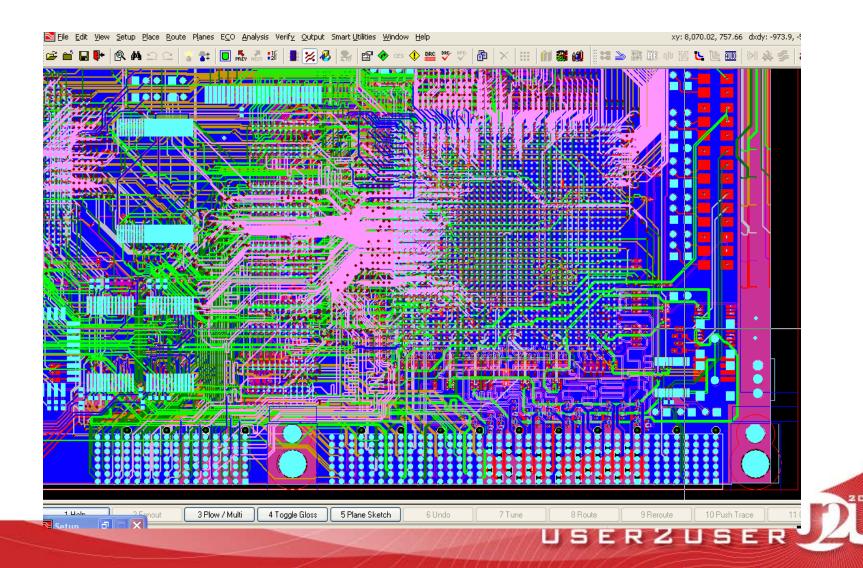

- CES Constraint rules for DDR3 and LVDS SERDES.

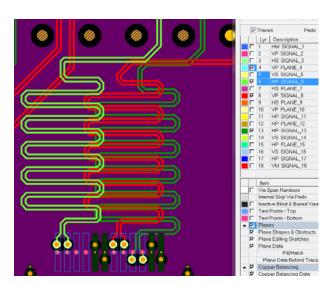

- Routing best practices for DDR3 and LVDS SERDES.

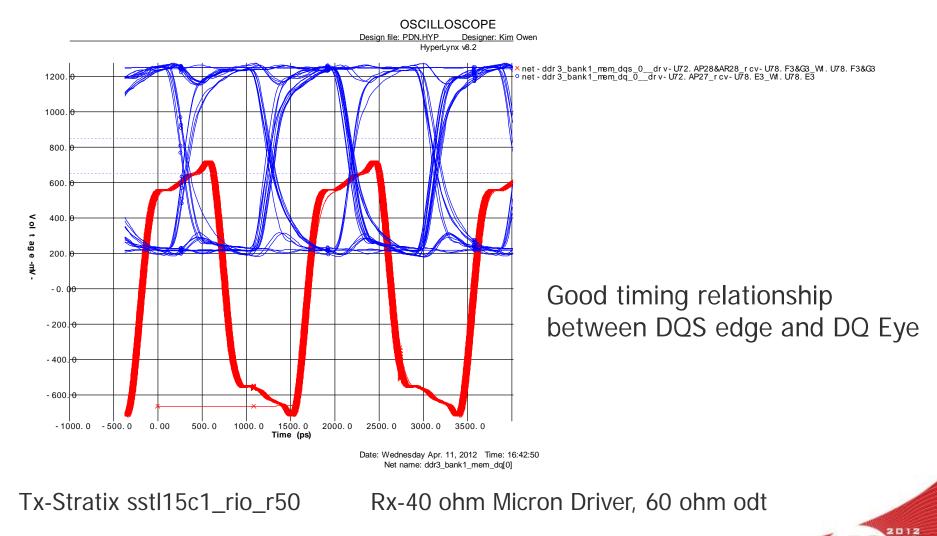

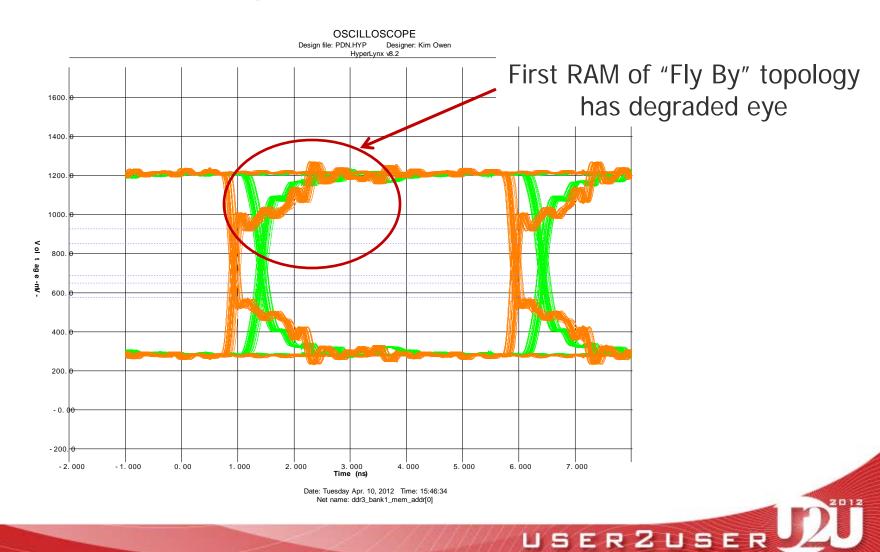

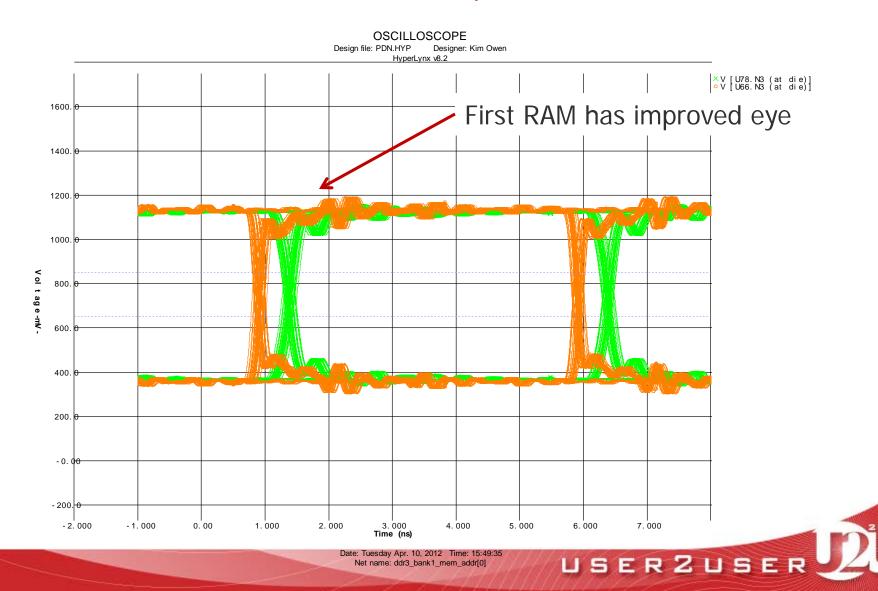

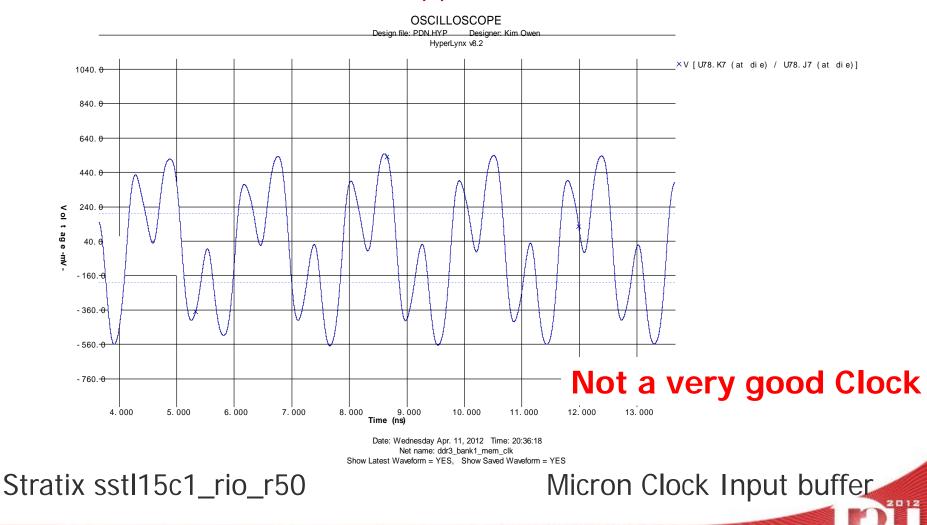

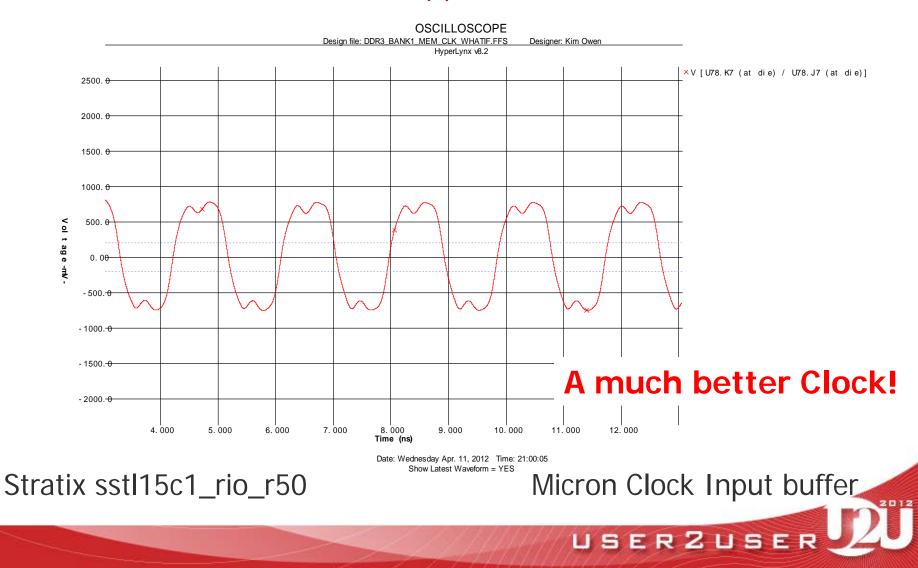

- HyperLynx performance analysis by simulation (Eye Diagrams).

USERZUSE

Class information

#### **DDR3 Design**

USERZUSER

2012

# "Without saying too much, PDN is a very good example of success story"

"Meticulous electrical design, perfect PCB design according to strict design rules and accurately tuned high speed traces gave us a perfect board.

Talking about DDR-3: as you probably recall, the architecture of PDN includes two banks of DDR3 memories, 64-bits each. My goal was operating the memories at about 400MHz (800Mbps). I have tested the board at maximum supported speeds (FPGA limited) of 533MHz (1067 Mbps): both banks are perfectly working with no issues. In addition, two High-Speed transceiver buses are perfectly running at 5Gbps per channel (overall data rate is 40Gbps), while 56 LVDS SERDES channels are running at 640Mbps.And, for the end, the first spin of the board is fully functional with no any electrical changes, blue wiring etc.

USERZUSE

The first revision is probably going to be the last one. "

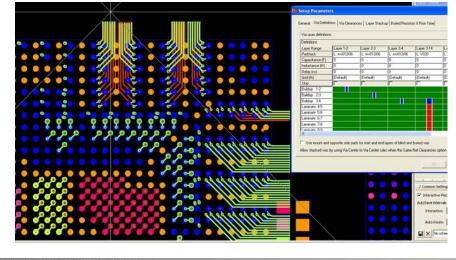

## Altera EP4SGX180 KF40C2N

| neral Via Definitio   | ons Via Clearance | es 🛛 Layer Stackup | Burie   | d Resistors | : & Rise Time |              |           |       |          |

|-----------------------|-------------------|--------------------|---------|-------------|---------------|--------------|-----------|-------|----------|

| Via span definitions: |                   |                    |         |             |               |              | * 4       | ż 🔊   | $\times$ |

| Layer Range           | Layer 1-2         | Layer 2-3          | Layer 3 | 2-17        | Layer 16-17   | Layer 17-18  | Through   | Via   | ~        |

| Padstack              | L: VC10P10D5      | L: VC10P10D5       | L: VC1  | 8P18D10     | L: VC10P10D5  | L: VC10P10D5 | L: VC22F  | 22D12 |          |

| Capacitance (F)       | 0                 | 0                  | 0       |             | 0             | 0            | 0         |       |          |

| Inductance (H)        | 0                 | 0                  | 0       |             | 0             | 0            | 0         |       |          |

| Delay (ns)            | 0                 | 0                  | 0       |             | 0             | 0            | 0         |       |          |

| Grid (th)             | (Default)         | (Default)          | (Defau  | dt)         | (Default)     | (Default)    | (Default) |       |          |

| Skip                  |                   |                    |         |             |               |              |           |       |          |

| Buildup 1-2           |                   |                    |         |             |               |              |           |       |          |

| Buildup 2-3           |                   |                    |         |             |               |              |           |       |          |

| Laminate 3-4          |                   |                    |         |             |               |              |           |       |          |

| Laminate 4-5          |                   |                    |         |             |               |              |           |       |          |

| Laminate 5-6          |                   |                    |         |             |               |              |           |       |          |

| Laminate 6-7          |                   |                    |         |             |               |              |           |       |          |

| Laminate 7-8          |                   |                    |         |             |               |              |           |       |          |

| Laminate 8-9          | -                 |                    |         |             |               |              |           |       |          |

Use mount and opposite side pads for start and end layers of blind and buried vias

Allow stacked vias by using Via Center to Via Center rules when the Same Net Clearances option is selected.

#### Xilinx U3 XC5VFX130T-1FF1738C | -SAT11255

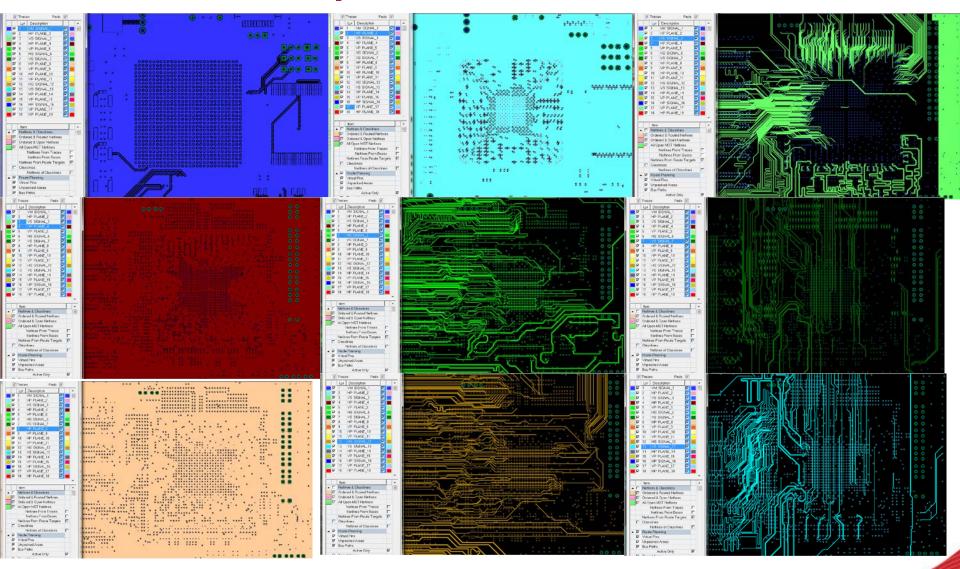

## **REVIEW OF HDI HIGH SPEED STACKUPS AND BENEFITS.**

#### **HDI Stackup Examples**

| Buildup 1-2       Image: Sector                                          | Grid (th)     | (Default) |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---|

| Buildup 2-3     Buildup 2-3     Buildup 3-4     Image 2-3     Image 2-3 <td< td=""><td>Skip</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Skip          |           |           |           |           |           |           |           |           |   |

| Buildup 3-4     Image of the second sec                           |               |           |           |           |           |           |           |           |           |   |

| Laminate 4-5       Laminate 5-6       Laminate 5-7       Laminate 5-7       Laminate 5-8       Laminate 1-1       Laminate 1-1 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |           |           |           |           |           |           |           |           |   |

| Laminate 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |           |           |           |           |           |           |           |           |   |

| Laminate 6-7 Laminate 7-8 Laminate 7-7 Lamin |               |           |           |           |           |           |           |           |           | _ |

| Laminate 7-8       Laminate 7-8       Image: 10 - 1       Image: 10 - 1 <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |           |           |           |           |           |           |           |           |   |

| Laminate 8-9       Laminate 9-10       Image: 10 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |           |           |           |           |           |           |           |           |   |

| Laminate 9-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |           |           |           |           |           |           |           |           |   |

| Laminate 10-1       Laminate 11-1       Laminate 11-1       Laminate 12-1       Laminate 13-1       Laminate 13-1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |           |           |           |           |           |           |           |           |   |

| Laminate 11-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Laminate 9-10 |           |           |           |           |           |           |           |           |   |

| Laminate 12-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Laminate 10-1 |           |           |           |           |           |           |           |           | = |

| Laminate 13-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Laminate 11-1 |           |           |           |           |           |           |           |           | _ |

| Laminate 14-1       Image: Control of                                         | Laminate 12-1 |           |           |           |           |           |           |           |           |   |

| Buildup 15-16     Buildup 16-17       Buildup 17-     Image: Constraint of the co                                                          | Laminate 13-1 |           |           |           |           |           |           |           |           |   |

| Buildup 15-16     Buildup 16-17       Buildup 17-     Image: Constraint of the co                                                          | Laminate 14-1 |           |           |           |           |           |           |           |           |   |

| Buildup 17-       Oefault)       (Default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Buildup 15-16 |           |           |           |           |           |           |           |           |   |

| Buildup 17-       Oefault)       (Default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Buildup 16-17 | -         |           |           |           |           |           |           |           |   |

| Skip       Image: Skip       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Buildup 17-   |           |           |           |           |           |           |           |           | * |

| Skip       Image: Skip       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Grid (th)     | (Default) | (Default) | (Default) | (Default) | (Default) | (Default) |           |           |   |

| Buildup 1-2     Buildup 2-3     Image: Constraint of the constraint                                    |               |           |           |           |           |           |           |           |           |   |

| Buildup 2-3       Image: Constraint of the second sec                                         |               |           |           |           |           |           |           |           |           |   |

| Laminate 3-4       Image: Sector                                         |               |           |           |           |           |           |           |           |           |   |

| Laminate 4-5       Image: 1 minite 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | -         |           |           |           |           |           |           |           |   |

| Laminate 5-6       Image: Constraint of the                                          | <u></u>       | -         |           |           |           |           |           |           |           |   |

| Laminate 6-7       Image: Constraint of the                                          |               | -         |           |           |           |           |           |           |           |   |

| Laminate 7-8       Image: Constraint of the                                          |               | -         |           |           |           |           |           |           |           |   |

| Laminate 8-9       Image: Second                                         |               | -         |           |           |           |           |           |           |           |   |

| Laminate 9-10       Image: Constraint of the second s                                         |               | -         |           |           |           |           |           |           |           |   |

| Laminate 10-1       Image: Constraint of the                                         |               | -         |           |           |           |           |           |           |           |   |

| Laminate 11-1     Image: Constraint of the constraint of t                           |               |           |           |           |           |           |           |           |           | - |

| Laminate 12-1       Image: Constraint of the second s                                         |               |           |           |           |           |           |           |           |           | = |

| Laminate 13-1     Image: Constraint of the constraint of t                           |               |           |           |           |           |           |           |           |           |   |

| Laminate 14-1     Image: Second                            |               |           |           |           |           |           |           |           |           |   |

| Laminate 15-1     Image: Second                            |               | _         |           |           |           |           |           |           |           |   |

| Buildup 16-17     Buildup 17-     Bu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |           |           |           |           |           |           |           |           |   |

| Buildup 17-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |           |           |           |           |           |           |           |           |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |           |           |           |           |           |           |           |           | - |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |           |           |           | 111       |           |           |           |           |   |

USERZUSER

Your Initials, Presentation Title, Month Year

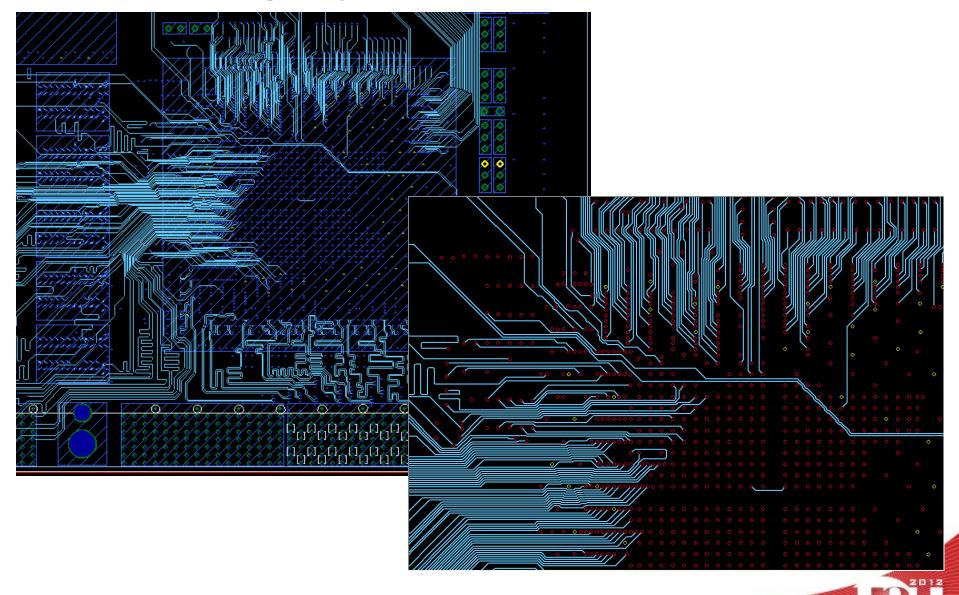

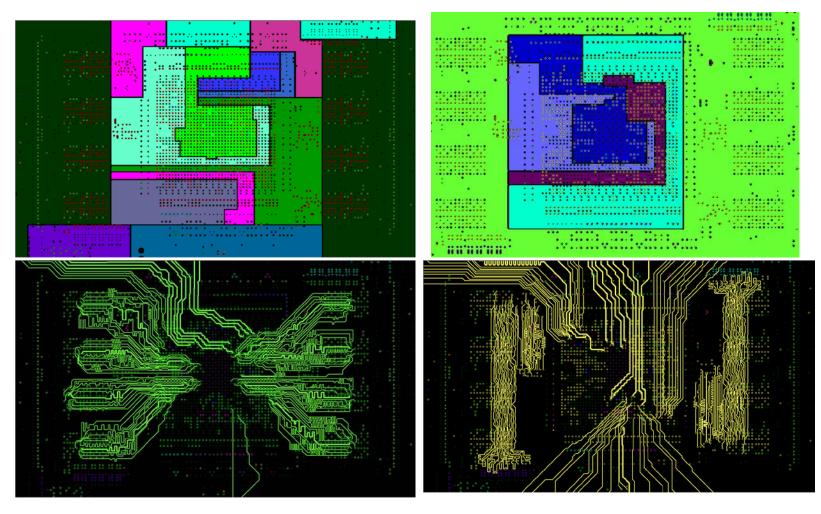

## **DDR3 Design HDI Stackup**

USERZUSER

2012

#### **HDI Benefits**

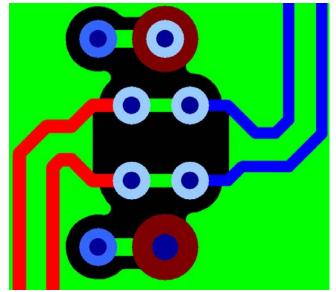

- The use of a custom microvia and core via structured breakout strategy for BGA's regions will assist in escape routing and increase power and ground planes

- Help eliminate via stubs when routing high speed nets

- Optimize discrete's placement, allowing room for breakouts and consider using microvia in pad for discrete parts with buried via combinations

- Create via grids to allow multi-channel routing in bga areas and over complete design wherever possible

- Create a stackup that allows the use of planes on outer 2 layers to pick up gnd and pwr connections

- With these combinations of routing and placement best practices and optimization techniques we will reduce layer count. PC board's could be routed with less signal layers if these routing and stackup strategies are implemented.

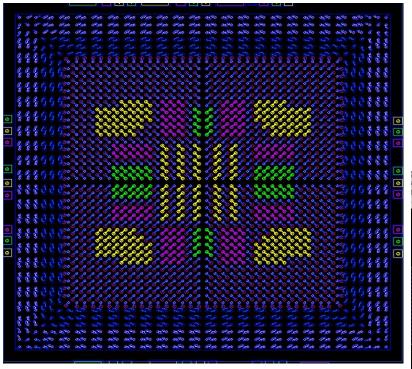

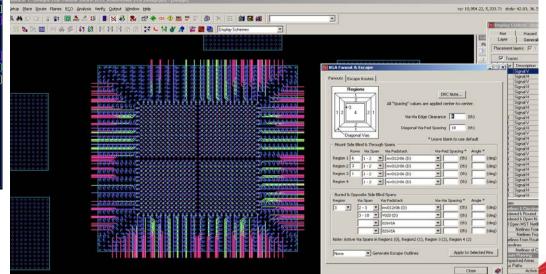

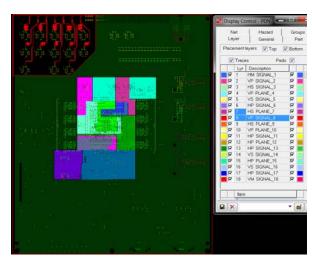

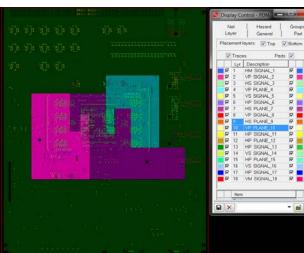

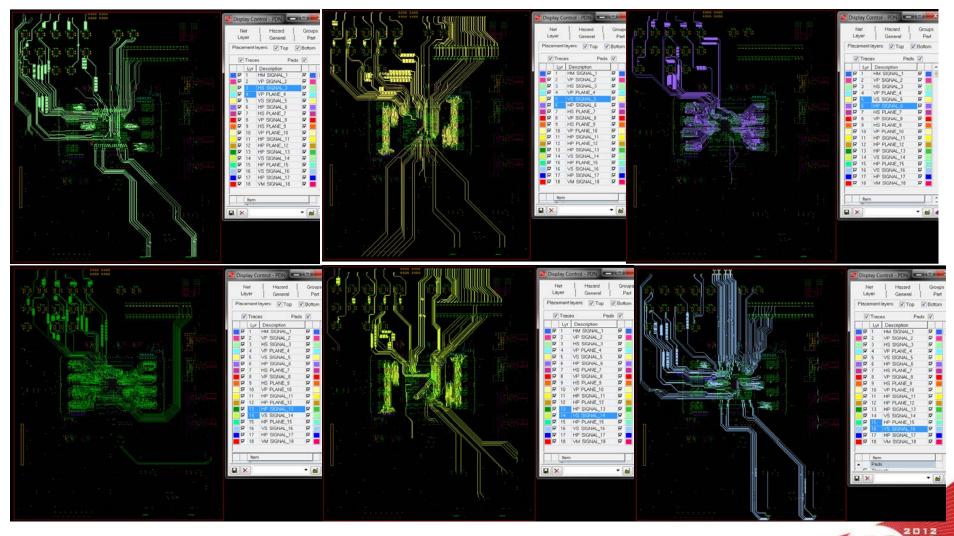

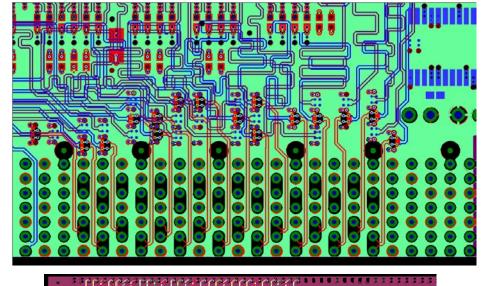

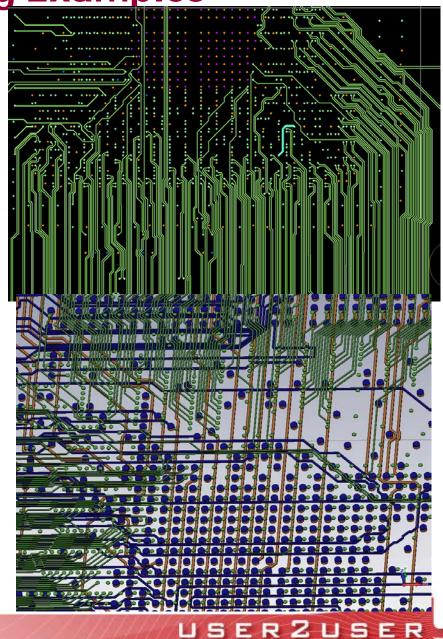

# HOW TO BREAKOUT HIGH PIN COUNT BGA'S

## Example Breakout and Escape Patterns

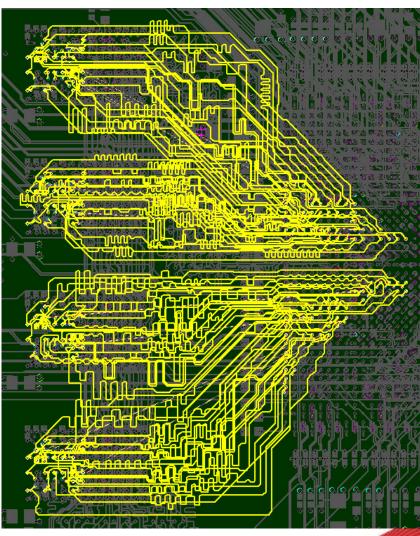

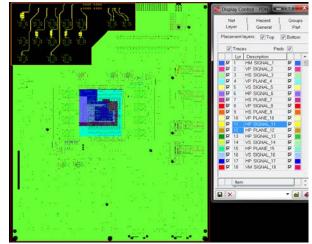

## HDI Routing Layer 3

# Microvia escape routing strategies will greatly enhance layer utilization

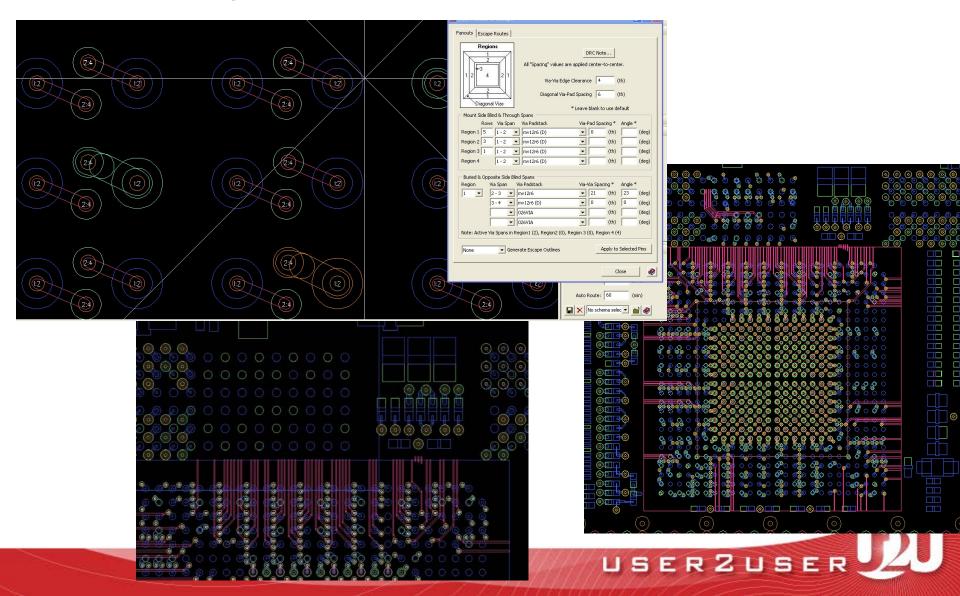

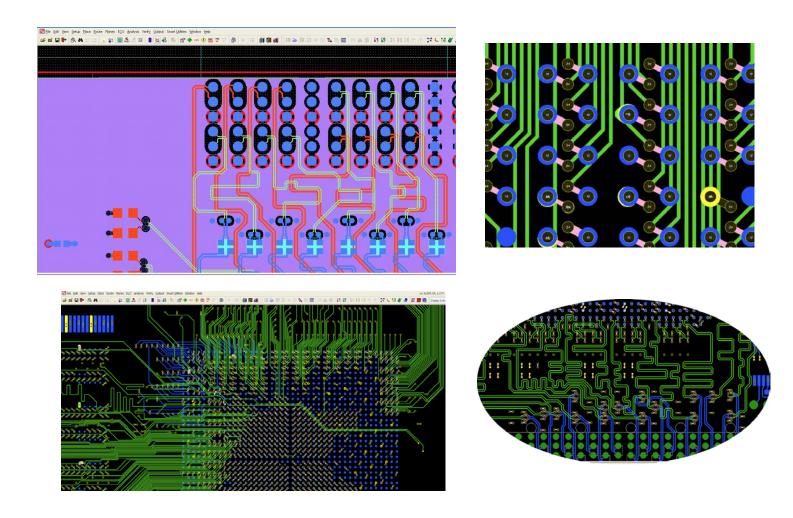

## IOD TECHNIQUES AND BEST PRACTICES

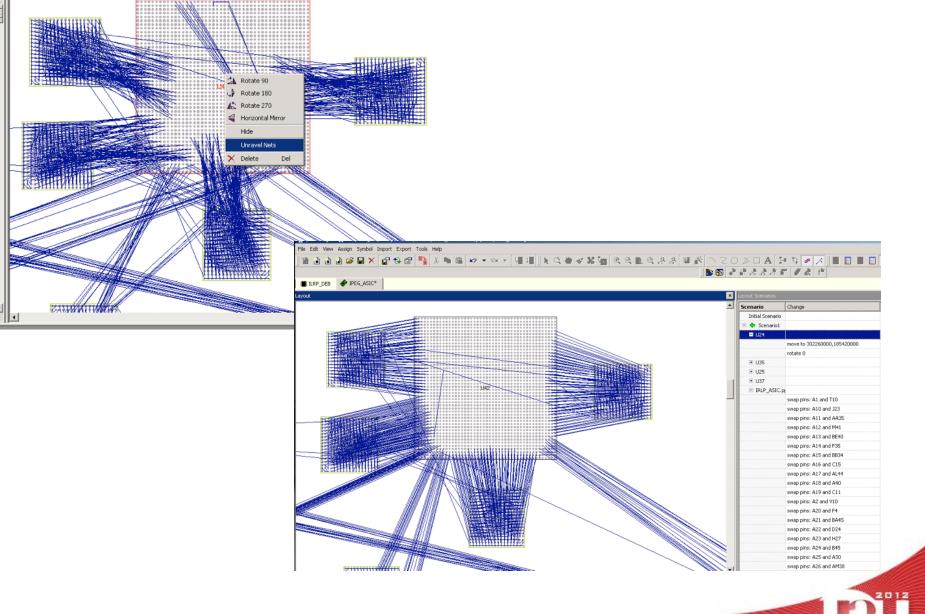

## **IO Designer Benefits**

- IO Designer can be used early in the PCB process and schematic creation; and during initial placement to unravel nets on high pin count BGA's

- Then again after breakout and escapes are created

- The use of IO Designer is a good way to accurately predict optimal layer count and stackup when considering high pin count BGA's

- IO Designer tool can be used to optimally route traces out of BGA fields.

- "Unraveling" done in banks automatically rather than manually one by one. A huge timesaver

- If the IOD strategy is implemented PCB design processes can be sped up significantly. A clear advantage for high density designs.

- To use IO Designer efficiently you must plan for it at the beginning and the IO Designer process must be followed

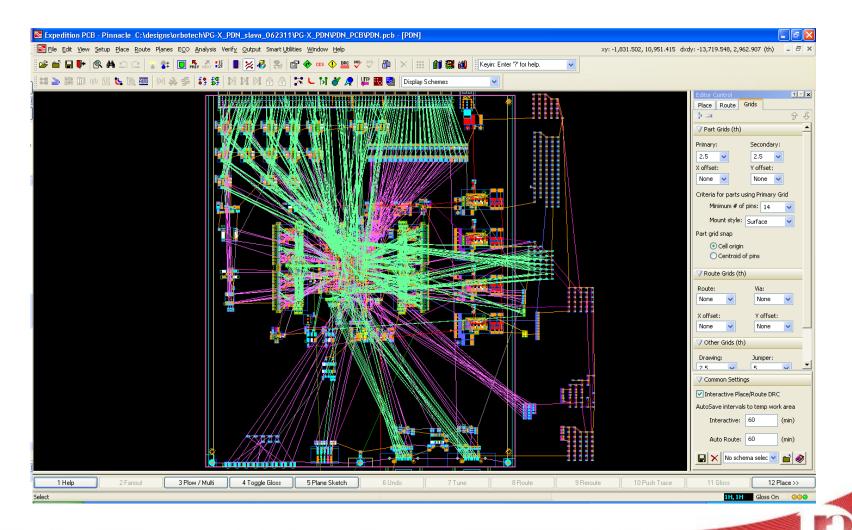

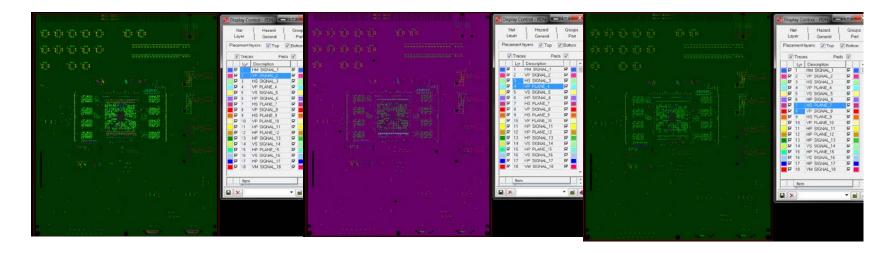

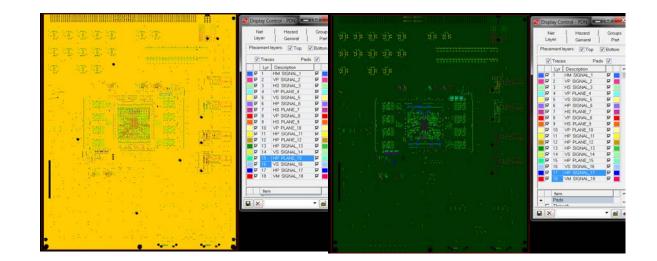

#### **Before Unravel**

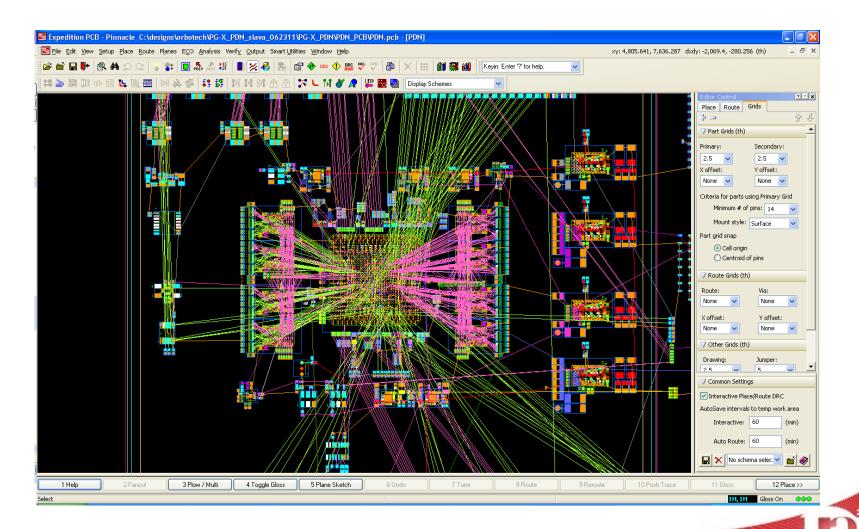

#### **DDR3 Design Unraveled Using IOD**

#### **IOD Screen Shot**

File Edit View Setup Assign Symbol Import Export Tools Help

| 💌 🔓 strata4x_06  |                                       |         |        |                      |      |     |                    |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|---------------------------------------|---------|--------|----------------------|------|-----|--------------------|----------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals          | ×                                     | Pins    |        |                      |      |     |                    | 4sgx180k f40c TOP&BC |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCB Name         | HDL Name $\bigtriangledown$           | Number  | Name   | Signal $ abla$       | Туре |     | J94                |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E AVLN1_rxin<3:  | DAVLN1_rxin<                          | ₩ AG19  | PAD314 | ddr3_bank1_mem_addr  |      | ▲ 🛔 | AnalogVCC<br>CLOCK | DQS DQSDIFF          | MGTRX<br>MGTTX | ▶ Temperatu<br>↑ VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ∃ AVLN1_txout <  | · · · · · · · · · · · · · · · · · · · | ₩ AH19  | PAD310 | ddr3_bank1_mem_addr  |      |     | CONFIG             | GND                  | ▲ NC           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | ) AVLN2_rxin<                         | ₩ AV19  | PAD301 | ddr3_bank1_mem_addr  |      | 0   | DIFF               | IO                   | PLL            | VCC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| E AVLN2_txout <3 | AVLN2_txout                           | ₩ AP20  | PAD306 | ddr3_bank1_mem_addr  |      |     |                    |                      |                | VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| E CARD_ID<2:0>   | CARD_ID<2:0                           | ₩ AH18  | PAD309 | ddr3_bank1_mem_addr  |      |     | DQ                 |                      | REFRES         | \$\$¥U#7 <i>///</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E CARD_VER<4:0   | CARD_VER<4                            | 10 AW18 | PAD322 | ddr3_bank1_mem_addr  |      |     | William .          | AUAN AY AEAA U       |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CX4_HTH_CH1      | CX4_HTH_CH                            | 10 AF19 | PAD316 | ddr3_bank1_mem_addr  | ·    |     |                    | 1                    |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CX4_HTH_CH2      | CX4_HTH_CH:                           | ₩ AW19  | PAD302 | ddr3_bank1_mem_addr  | IO   |     |                    |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CX4_LTH_CH1      | CX4_LTH_CH1                           | ₩ AV20  | PAD308 | ddr3_bank1_mem_addr  | IO   |     |                    |                      | 10             | 1011-02-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CX4_LTH_CH2      | CX4_LTH_CH2                           | 🎦 AU19  | PAD312 | ddr3_bank1_mem_addr  | IO   |     |                    |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CX4_PWEN_CH      | 1 CX4_PWEN_C                          | 🎦 AT19  | PAD311 | ddr3_bank1_mem_addr  | IO   |     | 1                  | 9                    | 19             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CX4_PWEN_CH      | 2 CX4_PWEN_C                          | 10 AV17 | PAD324 | ddr3_bank1_mem_addr  | IO   |     |                    |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E CX4_SPR_CH1    | CX4_SPR_CH:                           | ₩ AU17  | PAD323 | ddr3_bank1_mem_addr  | IO   |     |                    |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E CX4_SPR_CH2    |                                       | 🎾 AT20  | PAD304 | ddr3_bank1_mem_addr  | IO   |     |                    |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |